## **EE371**

# Advanced VLSI Design

## **Mark Horowitz**

Computer Systems Laboratory

Stanford University

horowitz@stanford.edu

Copyright 1999 Mark Horowitz

EE371 Lecture 1-1 Horowitz

## **Class Overview**

This class builds on EE313 and EE271 to look at the circuit design issues in large digital VLSI chips. At the core of this class is the job of 'circuit design' and the tasks that a circuit designer does in industry. As we will see, much of the current effort is directed at dealing with the wires, and various signal integrity issues.

Like EE271 we will look at large functional blocks; like EE313 we will use SPICE a lot. Since simulating a large function block in SPICE is not fun, much of the class will be devoted to building up ways of evaluating a circuit without having to simulate the whole thing. This skill is really the art of circuit design.

## **Class Readings**

I wish there was a good book on circuit design. But I have not found it yet. So the lecture notes are the principle reference material that you will use in the class. While the notes will cover the material in the class, they will not be as complete as the information that you would find in a textbook. Please let me know the areas that you would like to have more information. Since I should write a book on this subject eventually, it would help me to know what material is difficult.

To supplement these notes, I will also copy some key papers on circuit design issues. You are responsible for the material in these articles, even if we don't completely cover them in class. So it would be a good idea to read the papers before coming to class, and asking questions about the material you did not understand.

To provide additional information and/or an alternative explanation of the material in the notes, references to readings from other textbooks will be included in the notes. While these readings are not required, they are often helpful in understanding the material.

EE371 Lecture 1-3 Horowitz

## **Course Goals**

#### Dilemma:

While there are many techniques that don't work, there are also many techniques that work. Often it is hard to know what the "right" answer, since many approaches will solve the problem. The best solution often depends on the application and changes with time.

#### Goal:

This class will give you some tools that are needed to solve circuit design problems, and will provide you problems to practice using these tools. It will also provide examples of current design practice, so you can evaluate them and come to your own conclusions about their efficacy. This experimentation will help you with building the foundation you need to choose the appropriate circuits and verification methods to your problems.

EE371 Lecture 1-4 Horowitz

### Caveats

- 1. People lie. Sometimes intentionally, sometimes by accident, and sometimes it is because what you heard is not what they meant. Never take anything on blind faith. Work it out -- make sure it works. Many clever circuits that are published either don't work or are very sensitive to certain conditions. Be careful.

- 2. (Corollary to 1) Don't trust me. I am human too and have my bias and blind spots. I will try to tell you what I know, but I am not perfect, and so errors will appear. If you don't think what I am saying is correct, PLEASE let me know. I am from MIT and I can take it.

- 3. There are no RIGHT answers, and there are no PERFECT circuits. Everything has its warts. A good circuit simply has the right set of warts to meet the constraints of the problem.

- 4. Simulation is no substitute for thinking. SPICE can make your job much easier, but it also can make it much harder. Like all tools it helps only if you use it well. And that requires thinking.

EE371 Lecture 1-5 Horowitz

# **Class Topics**

First part of class will be focused on learning the fundamental tools:

- What to model / what to verify

- Device models, MOS and wires

- Worst-case design. Simulation methods. Margin testing

Next look at circuit families:

- From simple static CMOS to advanced forms

- What trade-offs that have been made

- What environments will the circuits function correctly

Then look at larger structures:

- Clocks and clock distribution

- Adders, multiplication, division, ...

- RAMs

- IO, including high-speed links (if we have time)

EE371 Lecture 1-6 Horowitz

## Logistics

#### Please come to class:

- I know it is televised, and on the internet, but if no-one comes to class, then no-one will ask me questions, and no-one will learn anything. I promise to be interesting, if you promise to attend lecture.

- And if people don't show up for class I will cut the in-campus broadcast

There is a review session for the class

- Every Friday at 2:15.

- This session should be televised, and on the internet too, if you can't make it. It will explain the homework (some more) and answer other questions that you have. It will review new tools that you can use for the class.

Tools used in this class

- Sue (schematic editor)

- HSPICE

EE371 Lecture 1-7 Horowitz

## Homework

There will be a number of weekly problem sets, and a final design project.

#### Homework:

- Handled out on Wednesday, due next Wednesday in class. No late assignments. Will give you a couple of day to look at assignment before the review session

- Homework will be to get experience with the technology and simulation and to experiment with new design techniques. There will usually be one, more openended design problem on each problem set.

- Grading the homework is hard. This year we are going to try something new. Each Thurs (or Friday) there will be a grading party, where the homework gets graded. Students in the class will be required to sign up for one grading party. At the party each student will get one problem, or part of a problem. The TAs or I will be around to help answer questions in grading. These students will then report back to the class on the variations in the solutions that were seen, by writing up a revised solution.

EE371 Lecture 1-8 Horowitz

## **HSPICE**

The problem sets will use a version of SPICE called HSPICE. This version has a number of features (like parameter sweeps and optimization) that will make your life easier. While the homework can be done with other versions of SPICE, please let me know if you don't have HSPICE available in your location. You will need to get approval from me to use another simulator.

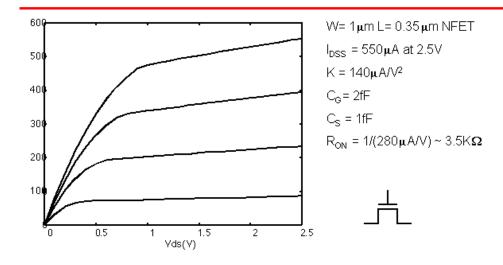

- There is a library provided for the class

- Consists of 'corner' models for a 0.35μ CMOS technology

- Wire models will also be provided

- Some of the assignments will require you to estimate parameters for a 'scaled' technology

- One of the review sessions on Friday will explain how to use the key features in HSPICE. I assume that you have all used it in EE313

FE371 Lecture 1-9 Horowitz

## **Project**

The project for this quarter is still a up in the air. There are two possibilities.

- Multifunction Multiplier Unit

- It would need to implement 64x64 multiplies, a 32x32 complex multiply (a+jb)(c+jd). It would also need to perform segmented multiplies (2-32, 4-16), and sum of absolute differences

- Router

A router for an on-chip multiprocessor that could be built in a  $0.1\mu$  technology. The idea is that there are 8x8 nodes; each node is 2mm x 2mm. Each router must source as many as 2 ports to the node, and it has two routing ports in each of the four possible directions.

Project will be done in groups of 2 people. You should find a partner that you can work with early in the quarter. Try to find someone you can work with and who complements your skills

EE371 Lecture 1-10 Horowitz

# Warning

This is a research project:

• I am planning on learning something from the results

#### Good news:

Many of my PhD students are interested in this problem

There is a seminar on Mondays

Experience with memory design / circuit trade-offs

#### Bad news:

• They do not know the 'right' answer either

You will need to make some circuit trade-offs

We will all be smarter by the end of the class

EE371 Lecture 1-11 Horowitz

## **Honor Code**

Please remember you are bound by the honor code:

- I will trust you not to cheat

- I will try not to tempt you

But if you are found cheating it is very serious

- There is a formal hearing

- You can be thrown out of Stanford

Save yourself and me a huge hassle and be honest

EE371 Lecture 1-12 Horowitz

# Lecture 1:

# Models, Simulation, and Circuit Design

# Computer Systems Laboratory Stanford University horowitz@stanford.edu

Copyright 1999 Mark Horowitz

EE371 Lecture 1-13 Horowitz

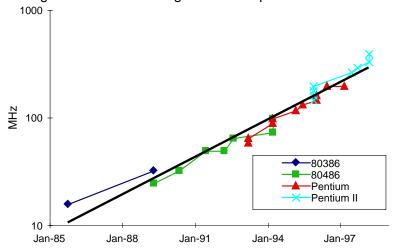

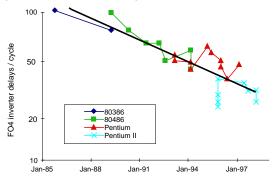

# **Integrated Circuit Trends**

Two trends have made circuit designers in high demand:

Process scaling and demands for high-clock rate processors

## What These Trends Mean

The cycle time of digital systems is falling faster than the speed of the gates

Need to build functions and wires that are faster (in terms of speed of the basic building blocks) than last time

Long wires are becoming wet noodles

- Pushing information through them is getting harder

- Need to worry about wire delay and noise coupling issues

EE371 Lecture 1-15 Horowitz

## **Faster Functions**

There are two approaches to building faster functions:

- Build faster logic gates

- Here you use some experience with transistors to craft faster basic gates

- Dynamic logic, and certain passgate logic is the best example of this

- Customize the layout to make the critical wires short

- Build faster architectures

- Leverage all those additional transistors that are possible

- Do more things in parallel, do some speculative calculations

- Decrease the time for the high-level function, by using many standard gates

The faster architecture approach is ALWAYS used, so digital circuit designers must deal with environments where there are a large number of gates and wires to deal with.

EE371 Lecture 1-16 Horowitz

## Example: Adder

#### Want to build a fast 64 bit adder:

- Look over the different architectures proposed

- Ripple, carry bypass, carry select,

- Tree adders

- Ling adder (reformulation of logic equations)

- Look over the circuit issues

- Static CMOS

- Pass transistor logic

- Dynamic Logic

- Number of stages of logic

- Clever implementation of individual logic gates, or groups of logic gates

EE371 Lecture 1-17 Horowitz

# Circuit Design

#### Most people think about:

- Innovative configurations of transistors that perform some function better.

- Where better might be smaller, faster, lower power, etc.

That is part of the job. The part that takes more time is:

Making sure that this collection of transistors will work

OR

Figuring out why this collection of transistors does not work, or only works on a few parts.

To do either, you need to be able to reason about circuits ...

EE371 Lecture 1-18 Horowitz

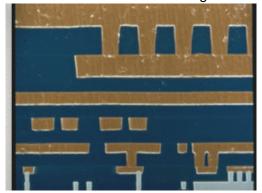

## The Problem

ICs are very complicated, contain many millions of tiny 3D structures

- Interleaving of conductors and insulators

- Diffusions of impurities in a semiconductor forming transistors

Could talk about the system in terms of 3D electric fields, and carriers

But takes a long time for a computer to simulate a single transistor

EE371 Lecture 1-19 Horowitz

# The Solution: Models

Need to use some kind of model to simulate anything

- In the 3-D simulation has some models for how the electrons behave

- This relies on other models for carriers in crystal structures

- Maxwell's equations

- Simulating complex designs mean that the base models must account for more effects in each element you 'model'

- Simulate transistors, not carriers

- Assume wires are equipotentials (quastatic models)

To reason about a system (either you or a machine) one needs a model of it.

EE371 Lecture 1-20 Horowitz

## **Models**

Are an approximation of the real world

- Must leave many details out

- Must (to be useful) retain the important 'details'

- Appropriate level depends on questions you want to answer

#### CAUTION:

- Simulation and analysis do not tell you what the circuit will do

- It tells you what your MODEL of the circuit will do

- So remember:

Garbage in, garbage out

Some of the hardest work is figuring out the right model for a problem

EE371 Lecture 1-21 Horowitz

# Modelling / Simulation Problem

There are really two problems:

- Need to generate the correct model of the circuit

- Need to stimulate that circuit in ways that exercise the problem

Add coupling noise the critical time

Set initial conditions for the worst-case charge-sharing

Inject substrate noise

#### SPICE limitation:

- Only evaluates the model of the circuit that you gave it

- Does the evaluation for the conditions you specify

Answers the question you ask,

But does not tell you whether it was the right question

EE371 Lecture 1-22 Horowitz

## What Model - The SPICE Approximation

Use lumped element model:

- Quasi-static (size is small compared to wavelength/4)

- Approximate devices by terminal characteristics

- Connections in the model are equipotentials

#### Major equation:

$$\bullet \ \, \left( \textbf{i} = \textbf{C} \cdot \frac{\Delta \textbf{V}}{\Delta \textbf{t}} \right) \rightarrow \Delta \textbf{t} \, = \, \frac{\textbf{C} \Delta \textbf{V}}{\textbf{i}} \quad \text{or} \quad \Delta \textbf{t} \, = \, \frac{\textbf{Q}}{\textbf{i}} \quad \text{charge control model}$$

So I need to model devices on the chip by their terminal iV and CV behavior -Figuring out the right model can be hard.

(Sometimes need inductor equation too)

EE371 Lecture 1-23 Horowitz

# What Needs to be Modeled?

#### **Transistors**

• nMOS, pMOS

#### Wires

- They are not ideal connectors

- How complex?

Resistance effects, iR drops in lines?

Coupling, Inductance?

#### Circuit Environment

- Temperature, Power Suppy, Substrate Voltage, Chip 'Gnd' vs Board 'Gnd'

- Modelling of the package and power and ground distribution nets

- Modelling of heat generation and flow

Appropriate model depends on question being asked

EE371 Lecture 1-24 Horowitz

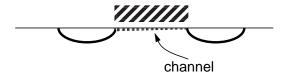

## **MOS Model Review**

#### For nMOS transistors

- Raising the gate voltage attracts electrons to form a thin n-region under the gate. Current in the transistor is controlled by the resistance of the channel region.

- Key to a good model is to understand what the device does NOT depend on:

- A MOS device depends on electric fields (Voltage/Length). If you keep this

constant, lots of stuff does not change (many of the 'short channel effects' are

not really dependent on the length, but rather depend on E-field)

EE371 Lecture 1-25 Horowitz

# **MOS** Review

Have already learned a number of different models for MOS devices

• Resistor Model, Quadratic Model, Velocity Saturated Model

## Transistor Models, cont'd

My favorite model for digital circuits is the simple resistor model

- Use simple RC to model timing

- Works well, even for complex devices

- Easy to think about

- But need to calibrate the 'resistance'

The resistance changes with

input slope, series devices, temp, fabrication, Vdd

Don't use quadratic model much

- Need to do a lot of fitting to get currents to match ok

- Use simplified velocity saturated model for current

Vds<sub>sat</sub> is when carriers are velocity sat, not Vgs-Vth

EE371 Lecture 1-27 Horowitz

## **Variations**

The characteristics of the elements are never exactly the same

Matching

Two identical transistor next to each other are slightly different Transistors on different sides of a die are less well matched Wires also can be mismatched

Processing variations

Widths and thickness of layers vary with each fabrication run Alignment of the layers is different with each run These differences mean transistor and wire properties change

Operating conditions

Temperature of the chip (or of the transistor) Voltage of the substrate, power supplies

EE371 Lecture 1-28 Horowitz

## **Device Modeling**

Since the devices are never the same, which one should we model?

- There is no right model

- Usually have a set of models that try to cover the range

- Your job is to choose the right model to test this circuit

Need to choose the one that will make it hardest for the circuit Murphy will ...

Remember it is your circuit

If you use the wrong models, your circuits will fail

Even if you used the models the fabrication guys gave you

Pays to make sure that the models make sense

Good to check iV curves against some real devices

EE371 Lecture 1-29 Horowitz

# **Scaling**

Scaling is driving the industry:

Assume you are making a device in the current technology in large volume. If you shrink that device to the new technology, although the new fab cost more to build, and thus is more expensive per mm<sup>2</sup>, since the device area scales, it will cheaper to make!

People scale to save money. It has a side effect of making the devices faster and lower power.

What happens when you scale a transistor?

```

L = \alpha L

```

$V = \alpha V$  (Vdd is now approximately equal to  $10V/\mu * L$ )

What happens?

E-fields remain roughly constant (many issues here)

Cap =

$$\alpha$$

Cap; Current =  $\alpha$  Current; V/i = constant

Delay =  $\alpha$  Delay

EE371 Lecture 1-30 Horowitz

# Scaling in the Real World

## Two problems:

Voltages don't always scale

Threshold voltage

Subthreshold leakage current

Interface standards

No longer an issue because of power

And high field stress

• Chips get more complex

Wires don't scale in length

So capacitance does not scale